Идем на RISC: альтернатива Intel и ARM

Содержание

- 1 Альтернатива Intel и ARM

- 2 Чем отличается RISC-V?

- 3 Жажда скорости

- 4 Компании уже используют RISC-V

- 5 11 мифов о RISC-V

- 5.1 Миф 1. RISC-V – это еще одна процессорная архитектура

- 5.2 Миф 2. RISC-V предназначен исключительно для научных целей, а не для промышленных приложений

- 5.3 Миф 3. На рынке нет ПЛИС или интегрированных сред разработки, которые можно использовать для оценки RISC-V

- 5.4 Миф 4. Для использования RISC-V необходимо приобретать платную лицензию

- 5.5 Миф 5. Компании, которые создают IP-ядра RISC-V, должны раскрывать их реализацию клиентам

- 5.6 Миф 6. Процессоры RISC-V не такие быстрые и эффективные как x86 или ARM

- 5.7 Миф 7. Не существует программных средств для работы с RISC-V

- 5.8 Миф 8. Несколько ядер RISC-V не могут работать совместно в одном процессоре. Они также не могут работать вместе с другими процессорами

- 5.9 Миф 9. Доверять ядру RISC-V опасно

- 5.10 Миф 10. RISC-V не поддерживаются ОС Linux

- 5.11 Миф 11. Невозможно перенести проект RISC-V с FPGA на ASIC

Если вы хотите создать компьютер с открытым исходным кодом, вы можете — если вы говорите о программном обеспечении. Однако процессор под капотом проприетарный. RISC-V — это процессор с открытым исходным кодом, который быстро набирает обороты и обещает сделать революцию в среде вычислений.

Альтернатива Intel и ARM

В настоящее время господствуют 2 конструкции процессоров: созданные ARM и Intel x86. Хотя обе компании работают в огромных масштабах, их бизнес-модели принципиально различаются.

Intel разрабатывает и производит свои собственные чипы, в то время как ARM лицензирует свои разработки сторонним разработчикам, таким как Qualcomm и Samsung, которые затем добавляют свои собственные улучшения. В то время как у Samsung есть инфраструктура для производства своих процессоров внутри компании, Qualcomm (и другие разработчики «без фабрики») передают эту важную работу сторонним организациям.

В случае ARM это также часто требует от лицензиаров подписания соглашений о неразглашении, предназначенных для сохранения конфиденциальности аспектов дизайна микросхемы. Это неудивительно, учитывая, что вся ее бизнес-модель построена не на производстве, а на интеллектуальной собственности.

Между тем, у Intel есть свои секреты коммерческого дизайна под замком. Поскольку оба типа процессоров являются коммерческими, разработчика трудно (если не сказать — полностью невозможно) повлиять на дизайн.

Чем отличается RISC-V?

RISC-V полностью другой. Во-первых, это не компания. Впервые он был задуман в 2010 году учеными Калифорнийского университета в Беркли как бесплатная альтернатива существующим компаниям с открытым исходным кодом.

Это похоже на установку Linux вместо Windows, поэтому вам не нужно ничего покупать или соглашаться с какими-либо обременительными лицензионными соглашениями. RISV-V стремится сделать то же самое для исследований и проектирования полупроводников.

ARM также лицензирует как архитектуру набора инструкций (ISA), которая относится к командам, которые изначально могут быть поняты процессором, так и микроархитектуру, которая показывает, как ее можно реализовать.

RISC-V просто предлагает ISA, позволяя исследователям и производителям определять, как они на самом деле хотят его использовать. Это делает его масштабируемым для устройств всех типов, от маломощных 16-битных чипов для встроенных систем с 128-битными процессорами для суперкомпьютеров.

Как следует из названия, RISC-V использует принципы компьютера с сокращенным набором команд (RISC), такие же, как и в микросхемах на базе ARM, MIPS, SPARC и Power.

Что это значит? Что ж, в основе любого компьютерного процессора лежат вещи, называемые инструкциями. Проще говоря, это небольшие программы, представленные на оборудовании, которые говорят процессору, что ему делать.

Микросхемы на основе RISC обычно содержат меньше инструкций, чем микросхемы, в которых используется компьютер со сложным набором команд (CISC), например, предлагаемые Intel. Более того, сами инструкции намного проще реализовать на оборудовании.

Более простые инструкции означают, что производители микросхем могут быть намного эффективнее при разработке своих микросхем. Компромисс в том, что эти относительно сложные задачи не выполняются процессором. Вместо этого они разбиваются программным обеспечением на несколько более мелких инструкций.

В результате RISC получил прозвище «Передача важных вещей компилятору». Хотя это звучит плохо, это не так. Однако, чтобы понять это, вы сначала должны понять, что такое компьютерный процессор.

Процессор в вашем телефоне или компьютере состоит из миллиардов крошечных компонентов, называемых транзисторами. В случае микросхем на основе CISC многие из этих транзисторов представляют различные доступные инструкции.

Поскольку чипы RISC содержат меньше простых инструкций, вам не нужно много транзисторов. Это означает, что у вас будет больше места для множества интересных вещей. Например, вы можете включить больше регистров кеша и памяти или дополнительные функции для AI и обработки графики.

Вы также можете сделать микросхему физически меньше, используя меньшее количество транзисторов. Вот почему чипы на основе RISC от MIPS и ARM часто встречаются в устройствах Интернета вещей (IoT).

Жажда скорости

Конечно, лицензирование — не единственное обоснование RISC-V. Дэвид Паттерсон, руководивший первыми исследовательскими проектами в области разработки процессоров RISC, сказал, что RISC-V был разработан для устранения надвигающихся ограничений производительности ЦП, которые могут быть достигнуты за счет производственных усовершенствований.

Чем больше транзисторов вы поместите в микросхему, тем более производительными в конечном итоге станет процессор. В результате производители микросхем, такие как TSMC и Samsung (которые производят процессоры от имени третьих сторон), прилагают все усилия, чтобы еще больше уменьшить размер транзисторов.

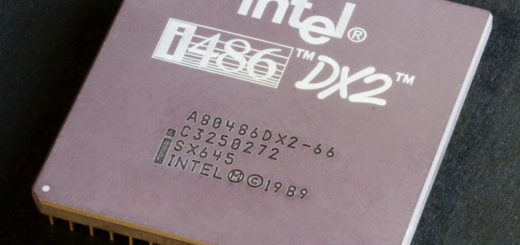

Первый коммерческий микропроцессор Intel 4004 имел всего 2250 транзисторов, каждый из которых имел размер 10 000 нанометров (около 0,01 мм). Маленький, конечно, но в отличие от процессора Apple A14 Bionic, выпущенного 40 лет спустя — этот чип (на котором работает новый iPad Air) имеет 11,8 миллиарда транзисторов, каждый размером 5 нанометров.

В 1965 году Гордон Э. Мур, соучредитель Intel, предположил, что количество транзисторов, которые можно разместить на кристалле, будет удваиваться каждые 2 года.

«Сложность, связанная с минимальной стоимостью компонентов, увеличивается примерно в два раза в год», — написал Мур в выпуске журнала Electronics, посвященном 35-летию.

«Конечно, в краткосрочной перспективе можно ожидать, что эта ставка сохранится, если не повысится. В более долгосрочной перспективе темпы роста несколько более неопределенны, хотя нет оснований полагать, что они не будут оставаться почти постоянными в течение как минимум 10 лет».

Ожидается, что закон Мура перестанет применяться в этом десятилетии. Также есть серьезные сомнения относительно того, смогут ли производители микросхем продолжить эту тенденцию к миниатюризации и дальше.

В конце концов, транзисторы меньшего размера намного сложнее и дороже в производстве. TSMC, например, потратила более 17 миллиардов долларов на свой завод по созданию 5-нм чипов. Учитывая эту «кирпичную стену», Risk-V стремится решить проблему производительности, ища способы помимо уменьшения размера и количества транзисторов.

Компании уже используют RISC-V

Проект RISC-V стартовал в 2010 году, а первый чип, использующий ISA, был изготовлен в 2011 году. Три года спустя проект стал публичным, и вскоре последовал коммерческий интерес. Технология уже используется такими компаниями, как NVIDIA, Alibaba и Western Digital.

Ирония заключается в том, что в RISC-V нет ничего революционного. Фонд отмечает на своей веб-странице:

«RISC-V ISA основана на идеях компьютерной архитектуры, которые возникли не менее 40 лет назад».

Что, возможно, является новаторским, так это бизнес-модель или ее отсутствие. Именно это делает проект открытым для экспериментов, развития и, возможно, неограниченного роста. Как отмечает на своем веб-сайте RISC-V Foundation:

«Интерес вызван тем, что это общий бесплатный и открытый стандарт, на который можно переносить программное обеспечение, и который позволяет любому свободно разрабатывать собственное оборудование для запуска программного обеспечения».

На момент написания этой статьи микросхемы RISC-V в основном работали негласно в серверных фермах и в качестве микроконтроллеров. Еще неизвестно, есть ли какой-либо потенциал встряхнуть дуополию ARM / Intel ISA в потребительском пространстве.

Тем не менее, если действующие игроки зайдут в тупик, вполне вероятно, что «темная лошадка» может выскочить и все изменить.

11 мифов о RISC-V

Давайте подробнее рассмотрим некоторые мифы, окружающие RISC-V ISA, чтобы лучше узнать технологию, инструменты и требования этой архитектуры, а также, чтобы понять каким образом ее можно использовать для ускорения инноваций и снижения затрат.

Миф 1. RISC-V – это еще одна процессорная архитектура

RISC-V – это стандартизованная, но открытая система команд (ISA). Она может быть расширена за счет дополнений, однако базовый набор команд является постоянным и не может быть изменен. В результате программа, написанная для одного ядра RISC-V с использованием базового набора команд, будет работать и на любом другом ядре RISC-V. Таким образом, использование открытой системы команд позволяет существенно ускорить внедрение новых решений и инновации. При этом компании могут оптимизировать и настраивать архитектуру под себя с учетом особенностей конкретных приложений. RISC-V должен сделать аппаратное обеспечение максимально открытым, как в свое время ОС Linux сделала открытым программное обеспечение.

Миф 2. RISC-V предназначен исключительно для научных целей, а не для промышленных приложений

Многие компании успешно внедряют RISC-V в своих коммерческих микропроцессорах. Andes Technology, Codasip, Bluespec, Cortus и другие поставщики встраиваемых IP-ядер предлагают реализации RISC-V. SiFive предлагает как лицензируемые программные IP-ядра, так и готовые, выполненные «в кремнии» микропроцессоры на базе RISC-V, в том числе и 32 -битную SoC-микросхему с RISC-V. Microsemi, Rumble Development и VectorBlox предлагают программные IP-ядра RISC-V, которые можно встраивать в FPGA. Например, на пятой конференции RISC-V 30 ноября 2016 года была показана полнофункциональная камера замедленной съемки, использующая ядро RISC-V, реализованное в ПЛИС IGLOO2.

Миф 3. На рынке нет ПЛИС или интегрированных сред разработки, которые можно использовать для оценки RISC-V

Компания Microsemi занимает лидирующее положение в этой области. Microsemi предлагает не только FPGA, поддерживающие ядра RISC-V (RTG4, IGLOO2 и PolarFire), но и интегрированную среду разработки (IDE) SoftConsole. Виртуальные платформы (программные симуляторы) также полезны для оценки RISC-V . Компания Imperas предлагает 32-битные и 64-битные модели ISA RISC-V и IDE (M*SDK) для разработки, отладки и тестирования программного обеспечения на RISC-V. Эти модели можно найти на веб-сайте Open Virtual Platforms. Кроме того, для оценки RISC-V разработчики могут использовать HiFive1 – Arduino-совместимую плату с RISC-V-процессором от SiFive.

Миф 4. Для использования RISC-V необходимо приобретать платную лицензию

Любой, кто хочет использовать RISC-V, может сделать это свободно – плата за использование RISC-V ISA не взимается. Например, многие программные ядра RISC-V можно бесплатно загрузить с сайта Microsemi, GitHub и др. Для конечных коммерческих продуктов использование товарного знака RISC-V или логотипа RISC-V разрешено только в соответствии с лицензией, предоставляемой в рамках Соглашения о членстве (RISC-V Foundation Membership Agreement.). Ключевым моментом является то, что данная ISA имеет разрешительную лицензию.

Миф 5. Компании, которые создают IP-ядра RISC-V, должны раскрывать их реализацию клиентам

Не существует каких-либо требований, согласно которым разработчик обязан раскрывать реализацию созданных им IP-ядер RISC-V ISA. Разработчик может поставлять IP-ядра RISC-V в закрытом виде в коммерческих продуктах, а может раскрывать их по-своему усмотрению. RISC-V Foundation поддерживает оба типа реализаций.

Кроме того, некоторые программные инструменты, поддерживающие RISC-V, включают в себя определенную реализацию IP-ядра. Как правило, эти инструменты, например, программы от Antmicro и Imperas, используют лицензию, аналогичную лицензии Berkeley Software Distribution (BSD) от Калифорнийского университета в Беркли; публичное раскрытие IP не требуется.

Миф 6. Процессоры RISC-V не такие быстрые и эффективные как x86 или ARM

Скорость и эффективность процессора зависит от множества параметров и особенностей реализации, в том числе от архитектуры, трассировки чипа, топологических норм производства и др. В теории процессоры RISC-V не уступают по производительности процессорам x86 или ARM. Наоборот, модульность ISA RISC-V позволяет создавать более эффективные решения, по сравнению с устаревшими системами команд x86 или ARM. Поскольку RISC-V ISA открыта, то у любого разработчика есть возможности для реализации максимально оптимизированного процессора для своих приложений.

Миф 7. Не существует программных средств для работы с RISC-V

Поддержка RISC-V была добавлена в GNU/GCC и GNU/GDB в мае 2017 года. Пользователям также предлагаются LLVM-инструменты (Low Level Virtual Machine) для создания компиляторов для RISC-V. Оба программных инструмента могут быть найдены на сайте RISC-V.

Antmicro предлагает для работы с RISC-V собственный симулятор инструкций (Instruction Set Simulator, ISS). Еще один симулятор инструкций есть в интегрированной среде разработки от QEMU. Imperas предлагает полностью виртуальную платформу для разработки программного обеспечения M * SDK. У Microsemi также есть среда IDE SoftConsole на базе Eclipse, которая используется для разработки программного обеспечения RISC-V.

SiFive предлагает бесплатную интегрированную среду разработки Freedom Studio на основе Eclipse.

Миф 8. Несколько ядер RISC-V не могут работать совместно в одном процессоре. Они также не могут работать вместе с другими процессорами

В этом смысле RISC-V ничем не отличаются от других процессорных ядер. Например, SiFive анонсировала многоядерные микросхемы с 32- и 64-разрядными ядрами RISC-V. В FPGA PolarFire для обеспечения расширенных функций безопасности микроконтроллер RISC-V используется совместно с криптографическим процессором Athena TeraFire. RISC-V отвечает за настройку типа безопасного обмена данными, а сам обмен осуществляет ядро TeraFire.

Миф 9. Доверять ядру RISC-V опасно

Если RTL-уровень (register transfer level) IP-ядра не закрыт и основан на хорошо известной открытой спецификации, его можно проверить и проанализировать, что важно для обеспечения безопасности проекта. При использовании программного IP-ядра RISC-V в FPGA можно самостоятельно проверить RTL, чтобы убедиться в его безопасности, в то время как в случае с процессорами с закрытыми архитектурами этого сделать нельзя, независимо от того идет ли речь о программных IP-ядрах или о готовых микросхемах. Таким образом, можно утверждать, что процессоры RISC-V с открытой реализацией оказываются намного более безопасным, чем ядра ARM или Intel, или любое другое закрытое программное ядро, где RTL недоступен.

Миф 10. RISC-V не поддерживаются ОС Linux

Наоборот, RISC-V поддерживаются несколькими разновидностями Linux, включая Yocto. В настоящий момент RISC-V Linux использует версию ядра Linux 4.6 и набор патчей RISC-V, которые будут включены в версию ядра 4.14. Это означает, что RISC-V скоро станет основной платформой в Linux. В отличие от ISA, создаваемых частными фирмами, открытый характер RISC-V ISA существенно облегчает координацию усилий различных компаний по поддержке Linux и других ОС, улучшая работу программного обеспечения и снижая затраты.

Миф 11. Невозможно перенести проект RISC-V с FPGA на ASIC

У некоторых производителей есть эмуляторы, которые позволяют предварительно запустить и проверить проект ASIC на FPGA. Codasip и SiFive предлагают прототипы IP-ядер для FPGA, которые можно перенести на ASIC. Microsemi предоставляет RTL для своих программных ядер RISC-V. Имея RTL очень просто сделать порт для ASIC, при этом не требуется оплачивать лицензионные отчисления.